The new file protection scheme protects big data files stored onboard the satellite against storage and transmission errors, which might occur in optical downlinks. This file protection is achieved through a novel packet level encoding scheme, which is applied offline to the whole file stored on-board the satellite. With this file protection, erroneous or deleted packets of the file can be corrected with a performance close to the theoretical limit (Singleton bound). The encoding and decoding of the file does not need complex computations and is dominated by read and write operations so that even a software implementation on a PC can achieve a high encoding/decoding speed of about 2 Gbit/s.

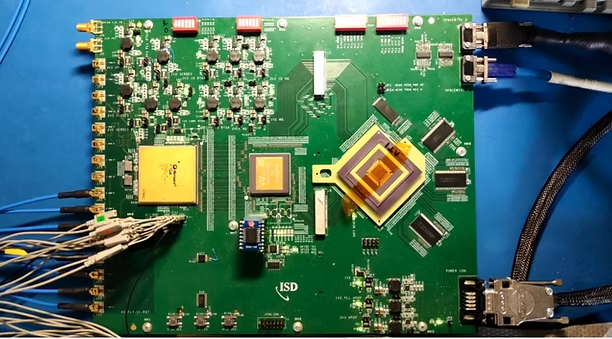

HPDP payload processing element is a high performance very versatile computational unit. The board contains two FPGAs that perform the routing and one HPDP chip which performs all the algorithm computations. The HPDP is composed of a systolic array and two serial CPUs that can work independently and can be programmed on-the-fly in a negligible time of around 40us.

Hi-SIDE data compression module

Application:

The high performance data processor will have application in on-board, high throughput, data processing for scientific, earth observation and telecom satellites.

Achievements:

HPDP implements a systolic array architecture, offering 40 GOps of computational capability with 1.65W power consumption. Within the Hi-SIDE project, ISD made the first attempt towards the development of a very low power, very low BOM, reconfigurable, ITAR-free, HPDP-based computational node. This is quite new for the European landscape and will enable more on-board computations in European satellites.