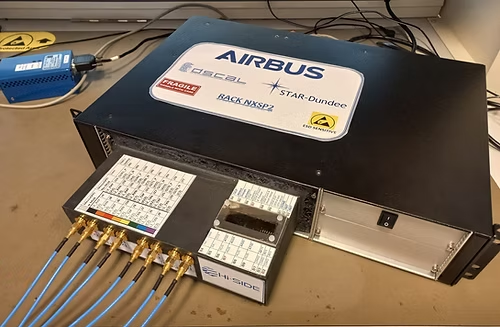

The Hi-SIDE data compression module is a powerful reconfigurable FPGA using SpaceFibre interfaces to connect to the on-board network.

Produced by Airbus Defence and Space, the data compression module provides a modular data compression system which can keep up with the very high instrument data rates foreseen for future missions.

To meet the needs of image compression electronic modules the compression module supports variable rate mass memory and telemetry. For 2D images, variable data rate CCSDS122-like compression is used. For fine spatial and spectral resolutions in 3D images, low complexity CCSDS 123.1-like compression is used, allowing multiple Gbps data rate range and lossless and near-lossless operation regimes.

For multispectral and hyperspectral (3D) images, a state-of-the art data-rate performance Hyperspectral Compression Engine (HCE) IP Core FPGA accelerator is developed by the Digital Systems and Computer Architecture Laboratory (DSCAL) of the National and Kapodistrian University of Athens (NKUA), based on the CCSDS 123.0-B-2 Low-Complexity Lossless and Near-Lossless Multispectral and Hyperspectral Image Compression algorithm, stemming from a cross-reference verified software implementation developed by Universitat Autònoma de Barcelona.

A single HCE can achieve 5Gbps while several HCE can be integrated and operating in parallel, taking advantage of CCSDS 123.0-B-2 segment-level parallelism, allowing for tens of Gbps data rate performance.

Application:

The data compression electronic board will have applications in a mix of new space and regular space situations. The board's versatility (FMC mezzanine and ability to reprogram) allows targeting of different applications with the same electronic board manufactured in higher quantities for lower costs.

Target Performance:

-

High data rate processing capabilities

-

SpaceFibre compliant interfaces

-

5 Gbit/s high performance compression

Hardware Achievements:

-

Extended 6U VPX format high throughput processing board based on cutting edge KU060 FPGA and DDR4 memory technologies

-

Application-oriented mezzanine for SpaceFibre interfaces.

-

FPGA development for infrastructure management and compression algorithm

-

Two parallel IP cores umplemented on-board, reaching 8.8 Gbit/s rate

HCE IP Core Achievements:

-

280 MSamples/s (4.4 Gbps@16bpppb).for a single HCE IP Core

-

1.25 GSamples/s (20 Gbps) for 5 HCE IP Cores

-

Scalability is only limited by available FPGA resources